This article was downloaded by:

On: 14 January 2011

Access details: Access Details: Free Access

Publisher Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37-

41 Mortimer Street, London W1T 3JH, UK

#### Molecular Simulation

Publication details, including instructions for authors and subscription information: <a href="http://www.informaworld.com/smpp/title~content=t713644482">http://www.informaworld.com/smpp/title~content=t713644482</a>

# A rigorous carrier-based analytic model for undoped ultra-thin-body silicon-on-insulator (UTB-SOI) MOSFETs

J. He<sup>a</sup>; W. Bian<sup>a</sup>; Y. Chen<sup>a</sup>; Y. Wei<sup>a</sup>; L. Zhang<sup>b</sup>; J. Zhang<sup>b</sup>; M. Chan<sup>c</sup>

<sup>a</sup> School of Computer and Information Engineering, Peking University Shenzhen Graduate School, Shenzhen, People's Republic of China <sup>b</sup> School of Electronic Engineering and Computer Science, Peking University, Bejing, People's Republic of China <sup>c</sup> Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Kowloon, Hong Kong

To cite this Article He, J. , Bian, W. , Chen, Y. , Wei, Y. , Zhang, L. , Zhang, J. and Chan, M.(2008) 'A rigorous carrier-based analytic model for undoped ultra-thin-body silicon-on-insulator (UTB-SOI) MOSFETs', Molecular Simulation, 34:1,63-72

To link to this Article: DOI: 10.1080/08927020701730393 URL: http://dx.doi.org/10.1080/08927020701730393

## PLEASE SCROLL DOWN FOR ARTICLE

Full terms and conditions of use: http://www.informaworld.com/terms-and-conditions-of-access.pdf

This article may be used for research, teaching and private study purposes. Any substantial or systematic reproduction, re-distribution, re-selling, loan or sub-licensing, systematic supply or distribution in any form to anyone is expressly forbidden.

The publisher does not give any warranty express or implied or make any representation that the contents will be complete or accurate or up to date. The accuracy of any instructions, formulae and drug doses should be independently verified with primary sources. The publisher shall not be liable for any loss, actions, claims, proceedings, demand or costs or damages whatsoever or howsoever caused arising directly or indirectly in connection with or arising out of the use of this material.

# A rigorous carrier-based analytic model for undoped ultra-thin-body silicon-on-insulator (UTB-SOI) MOSFETs

J. He<sup>abc</sup>\*, W. Bian<sup>a</sup>, Y. Chen<sup>a</sup>, Y. Wei<sup>a</sup>, L. Zhang<sup>b</sup>, J. Zhang<sup>b</sup> and M. Chan<sup>c</sup>

<sup>a</sup>School of Computer and Information Engineering, Peking University Shenzhen Graduate School, Shenzhen 518055, People's Republic of China; <sup>b</sup>School of Electronic Engineering and Computer Science, Peking University, Bejing 100871, People's Republic of China; <sup>c</sup>Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Clearwater Bay, Kowloon, Hong Kong

(Received 15 July 2007; final version received 6 October 2007)

This paper, presents a rigorous carrier-based analytic model for the long channel undoped (lightly doped) ultra-thin-body silicon-on-insulator (UTB-SOI) MOSFETs. It is based on the exact solution of the Poisson–Boltzamann equation coupled to the current continuity equation with the back interface oxide layer effect. The developed model is continuous and valid for all UTB-SOI MOSFET operation regions (linear, saturation, sub-threshold and strong inversion region) and traces the transition between different regions. This preliminary model has been verified by comparing with long channel results generated by 2D simulator. The predicted I–V characteristics also show in a good agreement with 2D numerical simulations for all ranges of gate and drain voltages, proving the validity of the analytical model. All these indicate that this model will be an ideal core model for UTB MOSFET compact modelling if the appropriate second-effects such as quantum mechanical effect, doping profile effect, short-channel effects and poly-depletion effect are integrated into it.

Keywords: non-classic CMOS; ultra-thin-body; silicon-on-insulator; device physics; compact modeling

#### 1. Introduction

The scaling of CMOS device and process technology, as it is known today, likely will end by the 10 nm node by 2020, following 2005 ITRS Roadmap [1]. The grand challenge, then, is to invent and develop one or more new technologies that will extend the scaling of information processing technologies through multiple generations beyond 2020. Under such a background, quantum devices, molecular electronics, nanotubes and new structures of non-classical CMOS have been proposed as possible alternatives of the traditional CMOS devices. Among these sub-10 nm scale devices, the ultra-thinbody silicon-on-insulator (UTB-SOI) is one of the most promising approaches for future CMOS scaling to feature sizes below 50 nm [2-5]. In contrast to other emerging device concepts UTB-SOI technology combines a planar transistor configuration with a superior sub-threshold slope resulting from a thin Si-body thickness of 5-40 nm. Together with reduced junction capacitances, high-k dielectrics, poly-SiGe gates or metal gates, these are attractive features for energy efficient CMOS logic operated at low supply voltages.

In recent years, the fabrication experiments and process improvements have been performed to explore the UTB-SOI MOSFET device characteristics and evaluate the UTB-SOI based circuit performance [1-3].

The numerical simulations have also been widely used to analyze the UTB-SOI device transport mechanism and design guideline although they are very time-consuming [4–10]. On the other hand, the compact modeling development on the UTB-SOI MOSFET has also been initialized in terms of the University Florid double-gate model (UFDG) by Fossum group [11] and further used to evaluate the circuit and device design [11–13].

In order to benchmark the circuit performance and optimize the layout structure based on UTB-SOI devices, there is a strong demand on a physics based compact model of UTB-SOI that can be implemented into the existing circuit simulation infrastructure. It is, however, very difficult to develop a physics-based analytic model for the UTB-SOI MOSFETs because of the unique physics effects of the non-classical UTB-SOI structure. Traditionally, the compact model of the MOSFET was developed based on the semi-empirical region approximation, such as the threshold voltage concept and the use of the saturation voltage. This method, however, has been thought to reach the limit of their usefulness and need to be replaced with the more advanced surfacepotential-based or inversion charge-based models [15]. A wide consensus in the compact modeling community is that the topology of the non-classical CMOS devices is fundamentally different from that of bulk or SOI devices,

thus results in the quite device physics pictures and new physics effects. The first is the quantum mechanical effect, which must be properly accounted for as it directly shifts the threshold voltage, degrades the gate capacitance of the device. Secondly, the charge sheet model, which has been the cornerstone of every bulk device compact model to date, is no longer a good approximation in thin film and double-gate devices. This is especially so with UTB structure in that when "volume inversion" takes place, the charge-sheet assumption breaks down. Furthermore, the structure of the nonclassical CMOS is fundamentally different from that of a bulk device since the multiple interfaces are involved to switch or bias. All these physical effects demand a new and unified physics-based approach to develop compact model for nanometer-scale CMOS devices. In fact, it is difficult to get the direct surface potential and inversion charge in the non-classical CMOS and the final channel current is always involving to the multiple interface potential and related spatial electrostatic potential [14]. If the short-channel effects such as the threshold voltage roll-off, drain-induced barrier lowering (DIBL) and velocity saturation and overshoot are involved, a complete compact model development will be a system project such as BSIM3/BSIM4 and take a long circle. In such a case, it is preferable to develop a physics based core model development for the long channel device and then the integration of more physics effects into it. We would like to stress that the most of the existing UTB-SOI models, however, have to rely on the charge-sheet approximation and some semi-empirical modeling concepts such as the threshold voltage and the smooth functions. The charge-sheet approximation cannot capture the volume inversion effect of the UTB-SOI, thus cannot predict the correct dependence of the subthreshold current and slope on the silicon film as demonstrated in Ref. [14]. On the other hand, the threshold voltage concept and smooth functions lead to the model region characteristics, accuracy and continuity issues as demonstrated the BSIM3/BSIM4 models in predicting the RF and analog circuit performance [15].

The recent research works on the non-classical CMOS in our group demonstrate that a carrier-based approach is a useful tool to develop the analytic yet continuous compact models for the double-gate MOS-FETs and cylindrical surrounding-gate devices [16–18]. For example, an approximated UTB-SOI MOSFET model has been presented based on a zero field assumption of the back interface in a recent work [19]. However, this assumption is not always satisfactory in general UTB-SOI MOSFET operation case. Thus, it may lead to some errors for thin back oxide layer and high gate voltage conditions.

Following the carrier-based modeling path, this paper presents a rigorous carrier-based analytic model based on

Poisson's equation solution and Pao-Sah double integral under the gradual channel approximation (GCA) for UTB-SOI MOSFETs. In our model development, the depletion charges in the silicon body are negligible for the UTB MOSFET because the silicon film is undoped (or lightly doped) and the threshold voltage is adjusted by the gate engineering. Under this reasonable approximation, only the mobile charge term is involved into Poisson's equation. As a result, the carrier-based continuous yet analytic model is derived for UTB-SOI MOSFETs directly from Poisson equation solution and Pao-Sah's double integral without the charge sheet approximation. It is shown that this analytic currentvoltage model covers all four regions of MOSFET operations: from the linear to the saturation, and from the sub-threshold to the strong inversion region, thus maintaining full continuity between different operation regions, and yet is completely physics based without any need for fitting parameters. The model has been validated by 2D numerical simulations, implying it is an ideal background for the UTB-SOI MOSFET compact model development if the appropriate short-channel effects, quantum effects, low and high field transport, noise and more are considered.

#### 2. Development of the rigorous analytic model

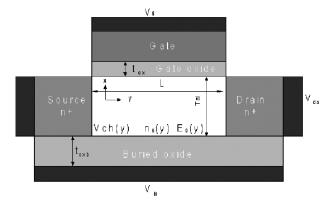

In present study, second order effects, such as the polysilicon depletion, doping impurity concentration profile and the quantum-mechanical effects are neglected for the sake of simplicity. Their exclusion, however, should not affect the general validity of the conclusions and it is possible to incorporate them without loss of generality for applications where they are significant. These problems will be discussed somewhere. Consider an undoped (or lightly doped) UTB-SOI as shown schematically in Figure 1. Under the GCA, Poisson's

Figure 1. Schematic diagram of an UTB-SOI MOSFET.  $V_{\rm ch}$  (y) is the quasi-Fermi potential at a point in the channel.  $\phi_0$  and  $n_0$  is the back surface potential and electron concentration, respectively.

equation along a vertical cut perpendicular to the Si film takes the formulation:

$$\frac{\mathrm{d}^2 \phi}{\mathrm{d}x^2} = \frac{q n_{\rm i}}{\varepsilon_{\rm si}} e^{q(\phi - V_{\rm ch})/kT} \tag{1}$$

With the Boltzmann statistics

$$n = n_{\rm i} \exp\left(\frac{q(\phi - V_{\rm ch})}{kT}\right)$$

and

$$n_0 = n_{\rm i} \exp\left(\frac{q(\phi_0 - V_{\rm ch})}{kT}\right). \tag{2}$$

Where q is the electronic charge, n is the induced electron concentration,  $\varepsilon_{\rm si}$  is the permittivity of silicon,  $n_i$  is the intrinsic carrier density,  $\phi(x)$  is the space potential,  $n_0$ ,  $E_0$  and  $\phi_0$  are the electron concentration, the electric field and the electrostatic potential at the back surface of the silicon film, the coordinate reference point as shown in Figure 1 and  $V_{\rm ch}$  is the electron quasi-Fermi Potential. Here, we consider an nMOSFET with  $q\phi/kT >> 1$  so that the hole density is negligible.

The spatial derivative of the electron concentration from (2) is written as

$$\frac{\mathrm{d}\phi}{\mathrm{d}x} = \frac{kT}{qn}\frac{\mathrm{d}n}{\mathrm{d}x} \tag{3}$$

$$\frac{\mathrm{d}^2 \phi}{\mathrm{d}x^2} = \frac{kT}{qn} \frac{\mathrm{d}^2 n}{\mathrm{d}x^2} - \frac{kT}{qn^2} \left(\frac{\mathrm{d}n}{\mathrm{d}x}\right)^2 \tag{4}$$

(1) is easily converted into the following equation in terms of the mobile electron following the Boltzmann statistics (2) and using the first and second-order spatial derivative of the electron concentration, Equations (3) and (4), respectively

$$\frac{\mathrm{d}^2 n}{\mathrm{d}x^2} = \frac{1}{n} \left(\frac{\mathrm{d}n}{\mathrm{d}x}\right)^2 + \frac{q^2 n^2}{\varepsilon_{\rm si} kT}.$$

(5)

Since, the potential  $\phi_0$  and electrical field  $E_0$  at the back interface of silicon body are always lower compared with that of the front interface because the back gate electrode is general ground or biased at the negative value. The field, potential and the electron distributions in the UTB-SOI MOSFETs should show a monotonic distribution from the front surface to the back surface. As a result, we can obtain the analytical potential, electron concentration and vertical field distribution from Equation (5). The normal differential Equation (5) has a universe mathematical solution for general UTB-SOI MOSFET structure, e.g. a hyperbolic function for the

ground or negative back gate biasing:

$$n(x - x_0) = \frac{c_0 c_1^2}{\sinh^2 \left[ \left( \frac{q^2 c_0}{2\varepsilon_{si} kT} \right)^{1/2} c_1 (x - x_0 + c_2) \right]}$$

(6)

where  $c_0$ ,  $c_1$  and  $c_2$  are the integration constants and  $x_0$  is the reference coordinate point, respectively.

If the choice of the reference coordinate point,  $x_0 = 0$ ,  $n(x_0) = n_o$ , is at the back surface, (6) is further simplified into

$$n(x) = \frac{n_0 c_1^2}{\sinh^2 \left[ \left( \frac{q^2 n_0 c_1^2}{2 \varepsilon_{si} kT} \right)^{1/2} \left( \frac{c_2}{c_1} + x \right) \right]}.$$

(7)

Substitution of (7) into the Poisson equation gives the corresponding electrical field and potential distributions in the silicon film

$$\phi(x) = V_{\text{ch}} + \left(\frac{kT}{q}\right) \ln\left[\frac{n_0 c_1^2}{n_i}\right] - \left(\frac{kT}{q}\right) \ln\sin h^2 \left[\left(\frac{q^2 n_0 c_1^2}{2\varepsilon_{\text{si}} kT}\right)^{1/2} \left(\frac{c_2}{c_1} + x\right)\right]$$

(8)

$$E(x) = -\left[\frac{2n_0c_1^2kT}{\varepsilon_{si}}\right]^{1/2} \coth\left[\left(\frac{q^2n_0c_1^2}{2\varepsilon_{si}kT}\right)^{1/2}\left(\frac{c_2}{c_1} + x\right)\right]. \tag{9}$$

If we define  $Q_{\rm in} = q \int_0^{T_{\rm si}} n(x) dx$ , the total inversion charge is obtained from the integration of Equation (7) along the vertical direction from x = 0 to  $x = T_{\rm si}$

$$Q_{\rm in} = -\left[2n_0c_1^2kT\varepsilon_{\rm si}\right]^{1/2} \, \coth\left[\left(\frac{q^2n_0c_1^2}{2\varepsilon_{\rm si}kT}\right)^{1/2}\left(\frac{c_2}{c_1} + T_{\rm si}\right)\right]$$

(10)

Of course, the surface potential and field are obtained from (8) and (9), respectively

$$\phi_{s} = V_{ch} + \left(\frac{kT}{q}\right) \ln\left[\frac{n_{0}c_{1}^{2}}{n_{i}}\right] - \left(\frac{kT}{q}\right)$$

$$\times \ln \sin h^{2} \left[\left(\frac{q^{2}n_{0}c_{1}^{2}}{2\varepsilon_{si}kT}\right)^{1/2} \left(\frac{c_{2}}{c_{1}} + T_{si}\right)\right]$$

(11)

$$E_{\rm s} = -\left[\frac{2n_0c_1^2kT}{\varepsilon_{\rm si}}\right]^{1/2} \coth\left[\left(\frac{q^2n_0c_1^2}{2\varepsilon_{\rm si}kT}\right)^{1/2}\left(\frac{c_2}{c_1} + T_{\rm si}\right)\right]. \tag{12}$$

The appropriate boundary conditions are used to determine the related constants. From (7) or (8), it is

easily found that both  $c_1$  and  $c_2$  have the relation

$$\sin h^{2} \left[ \left( \frac{q^{2} n_{0} c_{1}^{2}}{2 \varepsilon_{\text{si}} k T} \right)^{(1/2)} \frac{c_{2}}{c_{1}} \right] = c_{1}^{2}$$

(13)

From (13), we have

$$\left(\frac{q^2 n_0}{2\varepsilon_{si}kT}\right)^{1/2} c_1 c_2 = \sin h^{-1} c_1 \quad \text{or}$$

$$c_2 = \left(\frac{2\varepsilon_{si}kT}{q^2 n_0}\right)^{1/2} \frac{\sin h^{-1} c_1}{c_1}$$

(14)

Now, we need to determine the constant  $c_1$ . From (9) with x = 0, one obtains

$$E_0 = \left[\frac{2n_0kT}{\varepsilon_{\rm si}}\right]^{1/2} c_1 \coth\left[\left(\frac{q^2n_0}{2\varepsilon_{\rm si}kT}\right)^{1/2} c_1 c_2\right]$$

(15)

Substituting (14) into (15) gives

$$c_1 = \sqrt{\left(\frac{E_0^2}{\left\lceil \frac{2n_0kT}{\varepsilon_{\rm si}} \right\rceil}\right) - 1}.$$

(16)

Since the back gate is almost ground and the electric field must be terminated by zero or  $V_{\rm B}$  at the electrode, we have the boundary condition

$$V_{\rm B} - \Delta \phi_i - \phi_0 = -E_{\rm oxh} t_{\rm oxh}. \tag{17}$$

Thus,

$$E_{\text{oxb}} = \frac{\left[\frac{kT}{q} \ln\left(\frac{n_0}{n_i}\right) + V_{\text{ch}} + \Delta\phi - V_{\text{B}}\right]}{t_{\text{oxb}}}.$$

(18)

From the continuity principle of the electric flux, we can express  $E_0$  from (17)

$$E_{0} = \frac{\varepsilon_{\text{ox}}}{\varepsilon_{\text{si}}} \frac{\left[\frac{kT}{q} \ln\left(\frac{n_{0}}{n_{i}}\right) + V_{\text{ch}} + \Delta\phi - V_{\text{B}}\right]}{t_{\text{oxh}}}.$$

(19)

Equaling (16)–(18), we obtain  $c_1$ :

$$c_{1} = \sqrt{\frac{\varepsilon_{\text{ox}}^{2} \left[\frac{kT}{q} \ln \left(\frac{n_{0}}{n_{i}}\right) + V_{\text{ch}} + \Delta \phi - V_{\text{B}}\right]^{2}}{\varepsilon_{\text{si}}^{2} t_{\text{oxb}}^{2} \left[\frac{2n_{0}kT}{\varepsilon_{\text{si}}}\right]}} - 1. \quad (20)$$

In practice, the applied gate voltage controls the surface potential, field and the induced charges. According to Gauss law, the total applied gate voltage

is written as

$$V_{\rm G} - \Delta \phi_i = \phi_{\rm S} + E_{\rm ox} t_{\rm oxf} = \phi_{\rm S} + \frac{Q_{\rm in}}{\varepsilon_{\rm ox}} t_{\rm oxf}.$$

(21)

Substituting the surface potential and inversion charge expressions into (21) results in the solution of Poisson–Boltzmann equation in terms of  $n_0$

$$V_{\rm gs} - \Delta \phi - V_{\rm ch} = \frac{kT}{q} \ln \left[ \frac{n_0 c_1^2}{n_{\rm i}} \sinh^{-2} \left[ \left( \frac{q^2 n_0 c_1^2}{2\varepsilon_{\rm si} kT} \right)^{1/2} \right] \right]$$

$$\times \left( \frac{c_2}{c_1} + T_{\rm si} \right) \right] - \frac{t_{\rm oxf}}{\varepsilon_{\rm ox}} \left( 2n_0 c_1^2 \varepsilon_{\rm si} kT \right)^{1/2}$$

$$\times \coth \left[ \left( \frac{q^2 n_0 c_1^2}{2\varepsilon_{\rm si} kT} \right)^{1/2} \left( \frac{c_2}{c_1} + T_{\rm si} \right) \right].$$

$$(22)$$

Equation (22) gives an exact closed-form expression of the carrier electron concentration at the back interface of the silicon film as a function of the gate voltage, channel voltage and the silicon film. From the equation group of Equations (14), (20) and (22), the two constants  $c_1$  and  $c_2$  and the back interface electron concentration are calculated together yet simultaneously. As a result, The electron concentration, field and potential distribution and its surface value can be obtained precisely for calculated  $n_0$ ,  $c_1$  and  $c_2$ . This equation group is useful because of its exactness, solid physics background and the analytical characteristic in compact model construction.

For a given  $V_g$ ,  $n_0$ ,  $c_1$  and  $c_2$  can be solved from Equation (22) as a function of  $V_{\rm ch}$ . Along the channel direction (y),  $V_{\rm ch}$  varies from the source to the drain. So does  $n_0$  and  $c_1$ . If we define

$$z = \left(\frac{q^2 n_0 c_1^2}{2\varepsilon_{\rm si} kT}\right)^{1/2} \left(\frac{c_2}{c_1} + T_{\rm si}\right). \tag{23}$$

The functional dependence of z(y) and  $V_{\rm ch}(y)$  is determined by the current continuity condition which requires the current  $I_{\rm ds}=\mu WQ_iV_{\rm ch}/{\rm d}y={\rm constant},$  independent of V or y. Following Pao-Sah double integral [20], integrating  $I_{\rm ds}{\rm d}y$  from the source to the drain and expressing  $V_{\rm ch}/{\rm d}y$  as  $({\rm d}V_{\rm ch}/{\rm d}z)({\rm d}z/{\rm d}y)$ , the drain current is written as

$$I_{\rm DS} = \mu \frac{W}{L} \int_{0}^{V_{\rm ds}} Q_i(V_{\rm ch}) dV_{\rm ch} = \mu \frac{W}{L} \int_{z_{\rm s}}^{z_{\rm d}} Q_i(z) \frac{dV_{\rm ch}}{dz} dz.$$

(24)

Where  $z_s$  and  $z_d$  are solutions of (22) corresponding to  $V_{\rm ch} = 0$  and  $V_{\rm ch} = V_{\rm ds}$ , respectively. Note that the  ${\rm d}V_{\rm ch}/{\rm d}y$  can also be expressed as a function of z by differentiating (22). Substituting these factors into (23),

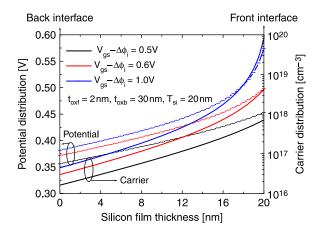

Figure 2. Predicted channel potential and carrier concentration distribution from Equation (22) along X direction from the silicon–oxide front interface to the back interface for different gate voltage in undoped UTB-SOI MOSFETs with the midgap gates and  $V_{\rm ch}=0$ ,  $t_{\rm ox}=2\,{\rm nm}$ ,  $T_{\rm si}=20\,{\rm nm}$  and  $t_{\rm oxb}=30\,{\rm nm}$ .

this current integrating can be performed analytical to yield a closed-form drain current expression:

$$I_{\rm ds} = \frac{\mu W}{L} \frac{\varepsilon_{\rm si}}{(c_2/c_1 + T_{\rm si})} \left(\frac{2kT}{q}\right)^2 \times \left[z \coth z - \frac{1}{2}z^2 - \frac{t_{\rm oxf}\varepsilon_{\rm si}}{T_{\rm si}\varepsilon_{\rm ox}(1 + c_2/c_1T_{\rm si})} \left(\frac{z^2}{2} \coth^2 z\right)\right]_{z_{\rm s}}^{z_{\rm d}}.$$

(25)

### 3. Results and discussion

UTB SOI-MOSFET characteristics for all regions: from the linear to the saturation, and from the sub-threshold to the strong inversion region, can be generated from the continuous, analytic drain current solution (25). In order to test the analytic model we have simulated one long channel well-tempered UTB-SOI MOSFETs with the abrupt junction approximation of the source and drain end with 2D numerical simulations from the ULTRAS-SOI<sup>®</sup> [21], by turning-off the quantum mechanism, polysilicon depletion effect and the tunneling current effect for comparison with the analytical model. A constant effective mobility of 300 cm<sup>2</sup>/V-s has been used for all calculations either for the numerical simulation or the analytic prediction. The simulated UTB-SOI MOSFET has a channel length of 2 μm, width of 10 μm, silicon gate oxide thickness ( $t_{oxf}$ ) of 2 nm and the mid-gap gate, e.g.  $\Delta \phi_i = 0$ .

Figure 2 plots the predicted potential and carrier concentration distribution along the X direction from the silicon—oxide back interface to the front interface for different gate voltage from the exact solution of (22). It is

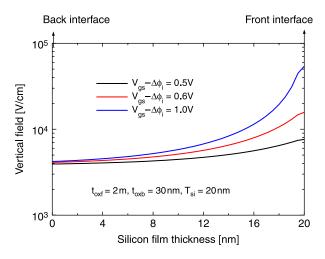

Figure 3. Vertical field distribution in the active silicon predicted by Equation (22) along X direction from the siliconoxide front interface to the back interface for different gate voltage in undoped UTB-SOI MOSFETs with the midgap gates and  $V_{\rm ds}=0$ ,  $t_{\rm ox}=2$  nm,  $T_{\rm si}=20$  nm and  $t_{\rm oxb}=30$  nm.

evident that the front interface potential and carrier concentration increase faster than that of the back interface with rise of the gate voltage. For example, the potential of the back interface increases from 0.355 to 0.38 V with the increase of the effective gate voltage from 0.5 to 1.0 V. In contrast, the potential of the front interface increases significantly, e.g. from 0.453 to 0.574 V for the corresponding gate voltage. As a result, the corresponding electron concentration of the back interface changes from  $1.6 \times 10^{16} \, \mathrm{cm}^{-3}$  to  $5 \times 10^{16} \, \mathrm{cm}^{-3}$  while that of the front interface increases from  $7 \times 10^{17} \, \mathrm{cm}^{-3}$  to  $8 \times 10^{19} \, \mathrm{cm}^{-3}$ . These results indicate that the contribution of the back interface to the performance of the UTB-SOI MOSFETs is always less than that of the front interface.

In order to further elucidate the effect of the back interface and the buried oxide layer in the UTB-SOI MOSFETs, Figure 3 illustrates the predicted field distribution along X direction from the silicon-oxide back interface to the front interface for different gate voltage based on the exact solution of (22). It is easily found that the front interface field is always larger than that of the back interface. With the increase of the effective gate voltage, the front interface electric field also increases fast while the back interface electric field has only a slight change. This results demonstrates that the UTB-SOI MOSFET behaves more like the half symmetric double-gate case in most cases except the fact the field of double-gate symmetric point is zero while the back surface field in UTB-SOI is not zero, but very small. This kind of similarity implies that the approximation of  $c_{1\rightarrow 1}$ , then  $c_{2\rightarrow 0}$  may be satisfied in UTB-SOI structures for the thick buried oxide layer and low gate voltage, as

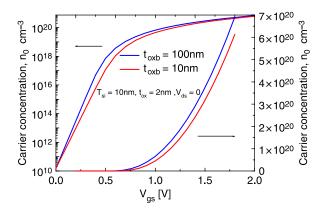

Figure 4. The calculated  $n_0$  versus gate voltage curve from Equation (22) for the different buried oxide thickness.

discussed in Ref. [19]. Thus, the zero back interface field approximation is an appropriate assumption for approximate compact model development as done in most SOI-MOSFET compact models. However, the real buried interface electric field is not zero for a practical UTB-SOI MOSFET device although it is always small, thus, a rigorous UTB-SOI model should model such a buried gate oxide existing, thus the buried interface field effect.

Figure 4 demonstrates the dependence of  $n_0$  versus gate voltage characteristics on the structure parameters, e.g. the buried oxide thickness, from the Equation (22). Similar to the inversion charge, the carrier concentration increases exponentially in the sub-threshold region. However, the electron carrier concentration is not a linear function of the effective gate voltage even in the strong inversion region.

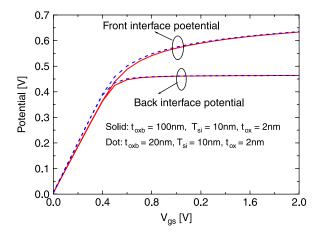

Figure 5 shows the calculated surface and the back interface potential dependence on the gate voltage for the different buried oxide layer thickness. Just like in a conventional MOSFET, there also exist two distinct regions of operation in the undoped UTB-SOI MOSFET, one is the sub-threshold region, where the surface and back interface potential is almost proportional to the gate voltage. Another is the strong inversion region, where the surface potential shows a logarithm increase with the gate voltage while the back interface potential is almost pinched off. One interesting observation is that the buried dielectric thickness has a slight effect on the potential distribution in the sub-threshold region, e.g. the surface and the back interface potentials increase with the decrease of the buried oxide thickness. The surface and the back interface potentials in the strong inversion region, however, are almost independent from the change of the buried oxide thickness in the undoped UTB-SOI MOSFETs, as shown in Figure 5.

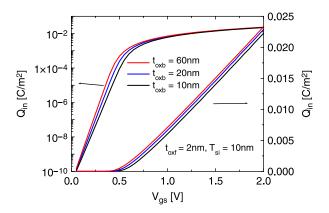

Figure 6 demonstrates the inversion charge density versus gate voltage curves for buried oxide thickness of 10-, 20- and 60-nm. It is found that the inversion charge

Figure 5. The calculated surface and back interface potentials versus the gate voltage in UTB-SOI MOSFETs from the analytic model for the different buried oxide thickness for  $V_{\rm ds}=0$ .

increases with the increase of the buried oxide thickness in both the sub-threshold and strong inversion regions. However, the inversion charge density gradually tends to a constant when  $t_{\rm ox}/t_{\rm oxb} \le 10^{-2}$ . An interesting result is that the sub-threshold slope of the UTB-SOI has a slight variation with the increase of the buried oxide layer thickness in this figure, which is consistent with the carrier concentration change as shown in Figure 2.

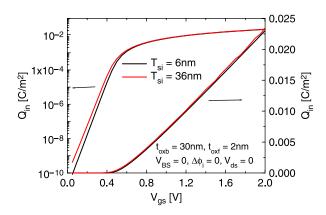

Figure 7 demonstrates the dependence of the channel inversion charge on the silicon body thickness, e.g. the "volume inversion" effect. It is found that the silicon film thickness only changes the amount of sub-threshold inversion charge but has a little effect on the strong inversion charge density. This verified the existence of the volume inversion and illustrates the volume inversion effect can be used to control the sub-leakage current in the used of UTB SOI–MOSFETs for nano-CMOS

Figure 6. Inversion charge density versus gate voltage for different buried oxide layer thickness in undoped UTB-SOI MOSFETs with the midgap gates for  $V_{\rm ds}=0$ .

Figure 7. Inversion charge density versus gate voltage for different silicon film thickness in undoped UTB-SOI MOSFETs with the midgap gates for  $V_{\rm ds}=0$ .

application, as the design of the non-classical MOSFET requires the use of the ultra-thin body.

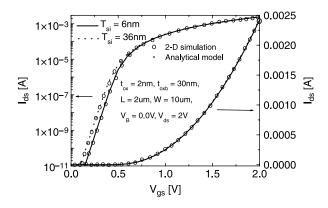

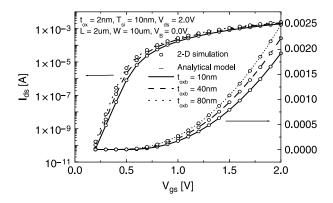

Figure 8 shows the good comparison of the transfer curve between the analytical model prediction and the numerical simulation result for 6- and 36-nm-thick body silicon film. There are two distinct regions of operation in this figure, both the sub-threshold and the strong inversion in UTB-SOI MOSFETs, just like in a conventional MOSFET. "volume inversion", in which the sub-threshold current is proportional to  $T_{\rm si}$ , is self evident in this figure. Again, the good agreement is observed. Note that the sub-threshold current is proportional to the silicon thickness—a manifestation of the "volume inversion" that cannot be reproduced by the standard charge-sheet-based models [22].

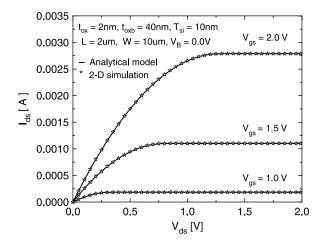

Figure 9 illustrates the good comparison of the transfer curve between the analytical model prediction and the numerical simulation result for the different buried oxide layer thickness. Figure 10 is  $I_{\rm ds}$ – $V_{\rm ds}$  curves calculated from the analytic model (solid curves),

Figure 8.  $I_{\rm ds}-V_{\rm gs}$  characteristics obtained from the analytic model for two different values of  $T_{\rm si}$  (solid and dashed curves), compared with the 2D numerical simulation results (symbols) for one UTB-SOI MOSFE with the mid-gap gate,  $\Delta\phi_i=0$ .

Figure 9. Plot of analytical  $I_{\rm ds}$  versus  $V_{\rm gs}$  with  $t_{\rm oxb}$  as a hidden parameter, compared with the 2D numerical simulation results (open circles) for one UTB-SOI MOSFET with the mid-gap gate,  $\Delta\phi_i=0$ .

compared with the 2D numerical simulation results (open circles). Both match well in both the linear and the saturation region. From the analytical model, one can find that both the inversion charge and the channel current are dominated by the last terms of Equations (22) and (25) in the linear region above threshold. In the saturation region, Equations (22) and (25) are dominated by the last terms for the source end while Equations (22) and (25) are, however, dominated by the first terms for the drain end. Here, the current approaches the saturation value infinitely with a term exponentially decreasing with the increase of  $V_{\rm ds}$ , in contrast to common piecewise models in which the current is constant in saturation without any change with the drain voltage.

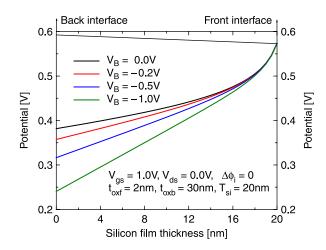

In practical CMOS devices, the substrate bias effect is an important device physics phenomena, which is used to control the device threshold voltage and improve the device performance. Thus, a physics based compact

Figure 10.  $I_{\rm ds}-V_{\rm ds}$  curves calculated from the analytic model (solid curves), compared with the 2D numerical simulation results (open circles) for UTB-SOI MOSFET with mid-gap gate,  $\Delta\phi_i=0$ .

Figure 11. Predicted channel potential distribution from Equation (22) along X direction from the silicon-oxide front interface to the back interface for different substrate bias voltage in undoped UTB-SOI MOSFETs with the midgap gates and  $V_{\rm ds} = 0$ ,  $t_{\rm ox} = 2$  nm,  $T_{\rm si} = 20$  nm and  $t_{\rm oxb} = 30$  nm.

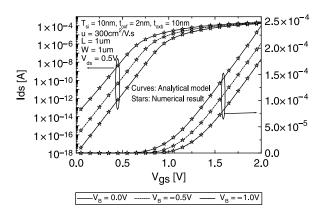

model should predict the correct body bias effect. Figure 11 plots the channel potential distribution along X direction from the silicon-oxide back interface to the front interface predicted by the presented analytic model for different  $V_{\rm B}$  when the front interface is in the strong inversion case with  $V_{\rm gs} = 1 \, \rm V$ . It is evident that the induced inversion charge screens the substrate bias effect on the front interface. Thus, the front interface potential keeps almost constant. In contrast, the back interface potential decreases with increase of the negative substrate bias voltage. This result also demonstrates the substrate bias effect on the UTB-SOI MOSFET performance, as shown in Figure 12. Again, the analytic results predicted by the presented model match very well the 2D simulation from the ALTRAS-SOI in this figures.

Figure 12. Plot of analytic  $I_{\rm ds}$  versus  $V_{\rm gs}$  with  $V_{\rm B}$  as a hidden parameter, compared with the 2D numerical simulation results (open circles) for one UTB-SOI MOSFET with the mid-gap gate,  $\Delta \phi_i = 0$ ,  $t_{ox} = 2$  nm,  $T_{si} = 10$  nm and  $t_{oxb} = 10$  nm.

One key physical effect neglected in the above analysis is the inversion layer quantum effect, which drives the peaks of electron concentration away from the front oxide interface and toward the center of the silicon film. How far the electron peak is from the surface depends on the magnitude of the surface electric field, i.e. charge density inside the silicon. As a result, the quantum effect will make the threshold voltage increase, subthreshold slope degradation with the reduction of the silicon film thickness. Moreover, the quantum effect will result in the gate capacitance decrease and the related silicon film thickness mobility. In general, for silicon film thickness much thinner than 5 nm, the quantum shift of due to the finite ground-state electron energy, which is inversely proportional to the square of the silicon thickness, becomes significant. Under those circumstances, it is difficult to control the UTB-SOI device performance because of its high sensitivity to the silicon thickness. However, for the compact model and circuit simulation, we can develop the separate quantum effect models to capture the variation of the threshold voltage, sub-threshold slope and mobility and then integrate them into a complete model framework as done for the international standard compact model of the bulk CMOS devices, e.g. BSIM3/BSIM4 in the past years. Similarly, the doping profile effect, short-channel effect and velocity saturation and overshoot can be modeled following a traditional path.

#### Conclusions

A carrier-based continuous analytic model for the long channel undoped UTB-SOI MOSFETs has been derived in this paper by solving the Poisson-Boltzmann equation coupled to the appropriate boundary conditions. All the regions of operation and the transitions of the UTB-SOI MOSFETs are correctly described by the single set of the carrier equations. In particular, the volume inversion that cannot be captured by using the charge-sheet approximation is well accounted and the effect of the buried oxide layer on the inversion charge and channel current is demonstrated in the detail by this model. It is also shown that the predicted current-voltage characteristics coincide with 2D numerical simulation results without any need for fitting parameter. This model will be useful for us to develop a complete compact UTB-SOI MOSFET model for circuit simulation if the appropriate secondeffects such as quantum mechanical effect, short-channel effects, and poly-depletion effect are integrated into it.

# Acknowledgements

This work is supported by the special funds for major state basic research project and the National Natural Science Foundation of China (NSFC: 90607017). This work is also partially supported by the International Joint Research Program (NEDO Grant) from Japan under the Project Code NEDOO5/06.EG01.

#### References

- Y.K. Choi, K. Asano, N. Lindert, V. Subramarian, T.J. King, J. Bokor, and C. Hu, *Ultrathin-body SOI MOSFET for deep-sub-tenth micron era*, IEEE Electron Device Lett. 21 (2000), pp. 254–255

- [2] K. Uchida, H. Watanabe, A. Kinosshita, J. Koga, T. Numata, and S. Takagi, Experimental study on carrier transport mechanisms in ultrathin body SOI n- and p- MOSFET with SOI thickness less than 5 µm, IEDM Tech. Dig. (2002), pp. 47–50.

- [3] T. Tezuka, N. Sugiyama, T. Mizuno, and S. Takagi, Ultrathin body SiGe-on-insulator pMOSFETs with high-mobility SiGe surface channels, IEEE Trans. Electron Devices ED-50 (2003), pp. 1328–1330.

- [4] J.H. Choi, Y.J. Park, and H.S. Min, *Electron mobility behavior in extremely thin SOI MOSFETs*, IEEE Electron Device Lett. 16 (1995), pp. 527–529.

- [5] D. Esseni, A. Abramo, L. Selmi, and E. Sangiorgi, Physically based modeling of low field electron mobility in ultrathin singleand double-gate SOI n-MOSFETs, IEEE Trans. Electron Devices TED-50 (2003), pp. 2445–2454.

- [6] R.J. Luyken, T. Schulz, J. Hartwich, L. Dreeskornfeld, M. Stadele, and W. Rosner, *Design considerations for fully depleted SOI transistors in the 25–50nm gate length regime*, Solid-State Electron. 47 (2003), pp. 1199–1203.

- [7] X. An, R. Huang, B. Zhao, X. Zhang, and Y. Wang, Design guideline of an ultra-thin body SOI MOSFET for low-power and high-performance applications, Semicond. Sci. Technol. 19 (2004), pp. 347–350.

- [8] C.G. Ahn, W.J. Cho, K.J. Im, J.H. Yang, I.B. Baek, S.K. Baek, and S.J. Lee, Recesseed source-drain (S/D) SO1 MOSFETs with low S/D extension (SDE) external resistance, IEEE International SO1 Conference, USA, October, 2004.

- [9] X. An, R. Huang, X. Zhang, and Y. Wang, Scaling of lowered source/drain (LSD) and raised source/drain (RSD) ultra-thin body (UTB) SOI MOSFETs, Solid-State Electron. 49 (2005), pp. 479–483

- [10] T. Schulz, C. Pacha, R.J. Luyken, M. Stadele, J. Hartwich, L. Dreeskornfeld, E. Landgraf, J. Kretz, W. Rosner, M. Specht,

- F. Hofmann, and L. Risch, *Impact of technology parameters on device performance of UTB-SOI CMOS*, Solid-State Electron. 48 (2004), pp. 521–527.

- [11] J.G. Fossum, L. Ge, M.-H. Chiang, V.P. Trivedi, M.M. Chowdhury, L. Mathew, G.O. Workman, and B.Y. Nguyen, *Process/physics-based compact model for nonclassical CMOS device and circuit design*, Solid-State Electron. 48 (2004), pp. 919–926.

- [12] S.-H. Kim and J.G. Fossum, Nanoscale CMOS: potential nonclassical technologies versus a hypothetical bulk-silicon technology, Solid-State Electron. 49 (2005), pp. 595–605.

- [13] C. Pacha, A. Schmal, T. Schulz, R. Gottsche, and W. Steinhogl, Evaluation of circuit performance of ultra-thin-body SOI CMOS, Solid-State Electron. 47 (2003), pp. 1205–1211.

- [14] SRC Research needs for semiconductor device compact modeling, Website: http://www.src.org (2003)

- [15] Y. Taur, X. Liang, W. Wang, and H. Lu, A continuous analytic drain-current model for DG MOSFETs, IEEE Electron Device Lett. 107 (2004), pp. 176–179.

- [16] J. He, X. Zhang, G. Zhang, and Y. Wang, Complete carrier-based non-charge-sheet analytic theory for nano-scale undoped surrounding-gate MOSFETs, IEEE International Symposium on Quality of electronic design, Proc. ISQED, San Jose, USA, March 2006.

- [17] J. He, M. Chan, X. Zhang, and Y. Wang, Carrier-based approach: a generous strategy to develop compact model of non-classical CMOS, IEEE of ICCDCS, Playa del Carmen, Mexico, April 2006.

- [18] J. He, M. Chan, X. Zhang, and Y. Wang, Complete carrier-based non-charge-sheet analytic model for nano-scale undoped symmetric double-gate MOSFETs, IEEE of EDSSC, Hong Kong, December 2005, pp. 247–252

- [19] J. He, M. Chan, G. Zhang, X. Zhang, and Y. Wang, A continuous analytic I-V model for long channel undoped ultra-thin-body Silicon-on-Insulator (UTB-SOI) MOSFETs from a carrier-based approach, Semicond. Sci. Technol. 21(1) (2006), pp. 261–266.

- [20] H.C. Pao and C.T. Sah, Effects of diffusion current on characteristics of metal-oxide (insulator)-semiconductor transistors, Solid-State Electron. 9 (1966), pp. 927–937.

- [21] U.L.T.R.A.S-S.O.I-1.0., A semiconductor device numerical simulator developed by the Group of Nanoscale and Terahtz Devices and Circuits of Peking University.

- [22] J.R. Brews, A charge sheet model of the MOSFET, Solid-State Electron. 21 (1978), pp. 345–352.